# Sequential Logic

## **Learning Objectives**

- 1. State the difference between combinational and sequential logic.

- 2. Identify rising and falling edges of a signal.

- 3. State the difference between edge triggered and level triggered circuit.

- 4. Complete timing diagrams for an SR latch, D latch, and D flip-flop.

## Combinational versus Sequential

There are two types of locks:

| Depends only on not the in which they were | Depends on the input $\begin{pmatrix} 35 & 0 & 5 \\ 30 & & & 10 \\ 25 & 20 & 15 \end{pmatrix}$ | _:<br>  |

|--------------------------------------------|------------------------------------------------------------------------------------------------|---------|

|                                            | always give the same output for a given set of inpu                                            | ts      |

|                                            | depend on the current state and the input. Therefo                                             | <br>re, |

|                                            | They are used to                                                                               |         |

|                                            | (S-R) Latch                                                                                    |         |

| Latches are                                | devices. They are sensitiv                                                                     | e.      |

| changes.                                   | sensitive: the output changes when the value of the input                                      |         |

|                                            | - value of Q becomes, regardless of previous value                                             |         |

|                                            | - value of Q becomes, regardless of previous value                                             |         |

| This logic circuit h                       | as two versions: active and active                                                             |         |

<sup>© 2019,</sup> Rebecca Rashkin - This document may be copied, redistributed, transformed, or built upon in any format for **educational**, non-commercial purposes. Please give me appropriate credit should you choose to modify this resource. Thank you:)

Active \_\_\_\_\_

Review - Nor Truth Table

| Symbol & Truth Table | If one of the inputs of a nor gate is 1, |

|----------------------|------------------------------------------|

|                      | the output must be                       |

|                      |                                          |

|                      |                                          |

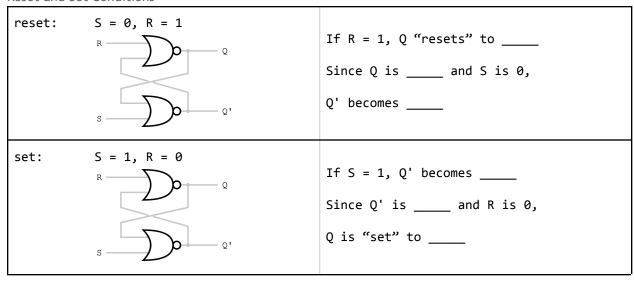

Reset and Set Conditions

Hold Condition, R = S = 0

We can't predict the output of a nor gate if we know only one of the inputs is  $\_$ \_\_\_. So for S = R = 0, we must know the initial values of Q & Q' to determine the outputs.

| S = R = 0, Q_init = 0, Q'_init = 1 | If Q is initially 0 and Q' is initially 1, then the output of the |

|------------------------------------|-------------------------------------------------------------------|

|                                    | nor gate stays,                                                   |

| ς Σρου ο'                          | and the output of the other nand gate                             |

|                                    | stays                                                             |

| S = R = 0, Q_init = 1, Q'_init = 0 | If Q is initially 1 and Q' is initially 0, then the output of the |

|                                    | nor gate stays,                                                   |

| s o'                               | and the output of the other nand gate                             |

|                                    | stays                                                             |

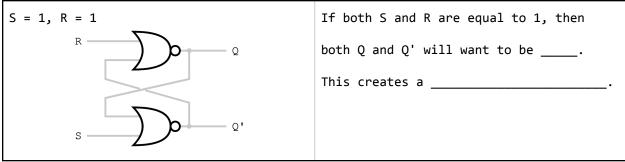

Invalid Input Combination: S = R = 1

Problem 1: Conflict

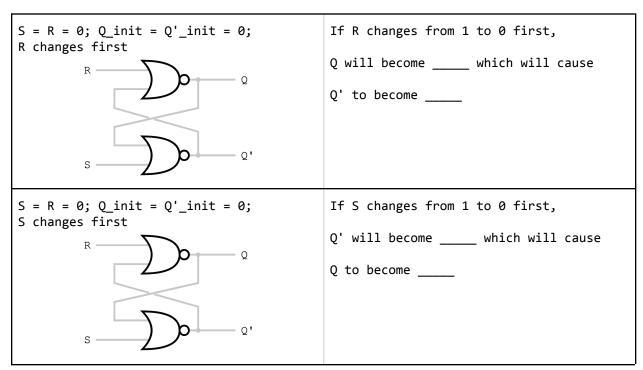

Problem 2: Race Condition

The final values of Q and Q' are \_\_\_\_\_\_ when changing from \_\_\_\_\_ to \_\_\_\_\_.

The \_\_\_\_\_ for a signal to travel through a wire is \_\_\_\_\_.

So, we cannot assume two signals can change at precisely the same time.

## Summary

| S | R | Q | Q' | Action |

|---|---|---|----|--------|

| 0 | 0 |   |    |        |

| 0 | 1 |   |    |        |

| 1 | 0 |   |    |        |

| 1 | 1 |   |    | •      |

|   |   |   |    |        |

Active \_\_\_\_\_\_ S-R Latch Timing Diagrams

Fill out Q and Q' for given S and R signals.

|    | ı |  |  |  |  |

|----|---|--|--|--|--|

| S  |   |  |  |  |  |

| R  |   |  |  |  |  |

| Q  |   |  |  |  |  |

| Q' |   |  |  |  |  |

| S  |   |  |  |  |  |

| R  |   |  |  |  |  |

| Q  |   |  |  |  |  |

| Q' |   |  |  |  |  |

| S  |   |  |  |  |  |

| R  |   |  |  |  |  |

| Q  |   |  |  |  |  |

| Q' |   |  |  |  |  |

Active \_\_\_\_\_

Review - Nand Truth Table

| Symbol & Truth Table | If one of the inputs is 0, |

|----------------------|----------------------------|

|                      | the output must be         |

|                      |                            |

|                      |                            |

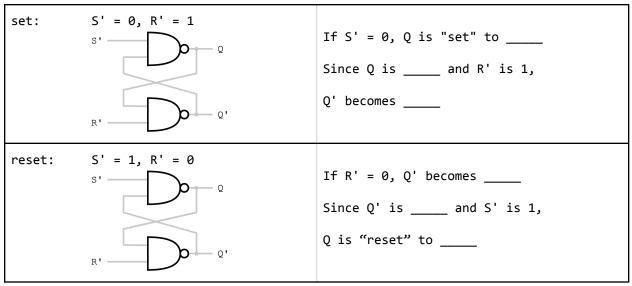

Reset and Set Conditions

Hold Condition, R' = S' = 1

We can't predict the output of a nand gate if we know only one of the inputs is  $\_\_$ . So for S'= R'= 1, we must know the initial values of Q & Q' to determine the outputs.

| S' = R' = 1, Q_init = 0, Q'_init = 1 | If Q is initially 0 and Q' is initially 1, then the output of the |  |  |  |  |  |

|--------------------------------------|-------------------------------------------------------------------|--|--|--|--|--|

|                                      | nand gate stays,                                                  |  |  |  |  |  |

| 8,                                   | and the output of the other nand gate                             |  |  |  |  |  |

| R'                                   | stays                                                             |  |  |  |  |  |

| S' = R' = 1, Q_init = 1, Q'_init = 0 | If Q is initially 1 and Q' is initially 0, then the output of the |  |  |  |  |  |

|                                      | , nand gate stays,                                                |  |  |  |  |  |

| 8,                                   | and the output of the other nand gate                             |  |  |  |  |  |

| R'                                   | stays                                                             |  |  |  |  |  |

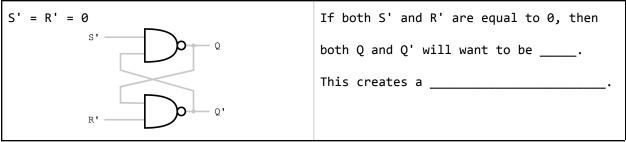

Invalid Input Combination: S' = R' = 0

Problem 1: Conflict

#### Problem 2: Race Condition

The final values of Q and Q' are \_\_\_\_\_\_ when changing from

\_\_\_\_\_ to \_\_\_\_\_.

As previously stated, we cannot assume two signals can change at precisely the same time.

<sup>© 2019,</sup> Rebecca Rashkin - This document may be copied, redistributed, transformed, or built upon in any format for **educational**, non-commercial purposes. Please give me appropriate credit should you choose to modify this resource. Thank you:)

Summary

| S' | R' | Q | Q' | Action |

|----|----|---|----|--------|

| 0  | 0  |   |    |        |

| 0  | 1  |   |    |        |

| 1  | 0  |   |    |        |

| 1  | 1  |   |    |        |

Active \_\_\_\_\_\_ S-R Latch Timing Diagrams

Fill out Q and Q' for given S' and R' signals.

| S' |  |  |  |  |

|----|--|--|--|--|

| R' |  |  |  |  |

| Q  |  |  |  |  |

| Ğ, |  |  |  |  |

|    |  |  |  |  |

| S' |  |  |  |  |

| R' |  |  |  |  |

| Q  |  |  |  |  |

| Q' |  |  |  |  |

|    |  |  |  |  |

| S' |  |  |  |  |

| R' |  |  |  |  |

| Q  |  |  |  |  |

| Q' |  |  |  |  |

### D Latch

| Draw the schematic here: |    |   |   |          |

|--------------------------|----|---|---|----------|

|                          | WE | D | Q | Q'       |

|                          |    |   |   |          |

|                          |    |   |   |          |

|                          |    |   |   |          |

|                          |    |   |   |          |

|                          |    |   |   | <u> </u> |

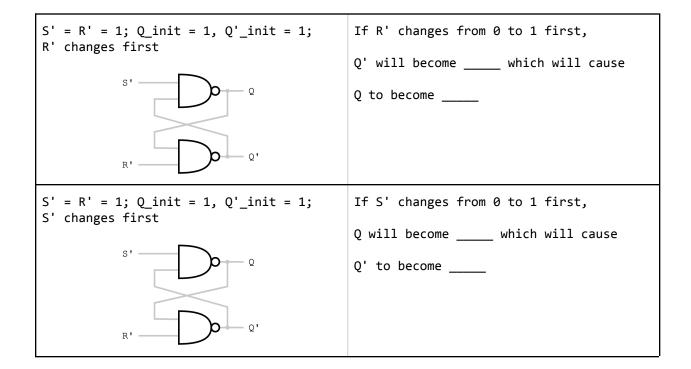

Timing Diagram Examples

Fill out Q and Q' for given WE and D signals.

|    |          |  | <br>_ |  |   |  |  |  |  |

|----|----------|--|-------|--|---|--|--|--|--|

| WE |          |  |       |  |   |  |  |  |  |

| D  |          |  |       |  |   |  |  |  |  |

| Q  |          |  |       |  |   |  |  |  |  |

| Q' |          |  |       |  |   |  |  |  |  |

|    | <u> </u> |  |       |  | l |  |  |  |  |

| WE |          |  |       |  |   |  |  |  |  |

| D  |          |  |       |  |   |  |  |  |  |

| Q  |          |  |       |  |   |  |  |  |  |

| Q' |          |  |       |  |   |  |  |  |  |

|    |          |  |       |  |   |  |  |  |  |

| WE |          |  |       |  |   |  |  |  |  |

| D  |          |  |       |  |   |  |  |  |  |

| Q  |          |  |       |  |   |  |  |  |  |

|    |          |  |       |  |   |  |  |  |  |

<sup>© 2019,</sup> Rebecca Rashkin - This document may be copied, redistributed, transformed, or built upon in any format for **educational**, non-commercial purposes. Please give me appropriate credit should you choose to modify this resource. Thank you:)

| D:         |          |           |           |           |           |          |                |           |           |            |

|------------|----------|-----------|-----------|-----------|-----------|----------|----------------|-----------|-----------|------------|

| Register   |          |           |           |           |           |          |                |           |           |            |

| A D latch  | is a de  | vice for  | storing   |           | A         |          | s <sup>-</sup> | tores se  | veral bit | īs.        |

| Draw a d   | iagram f | or a regi | ster:     |           |           |          |                |           |           |            |

|            |          |           |           |           |           |          |                |           |           |            |

| Clock      |          |           |           |           |           |          |                |           |           |            |

| The        |          | for a     | signal    | to trave  | l throug  | h a wire | is             |           |           | <b>_</b> · |

| For this   | reason,  | a         | is ι      | used to _ |           |          | sign           | nals in a | a compute | ∍r.        |

| A clock i  | s a free | -running  |           |           |           |          |                |           | sigr      | nal        |

| with a fi  | xed      |           |           |           |           |          |                |           |           | <u>_</u> . |

| The        |          |           | of a      | a clock i | s the     |          |                |           |           | _•         |

| Draw a c   | lock sig | nal. Labe | el the ri | sing edg  | ge, falli | ng edge, | and per:       | iod.      |           |            |

| CLK        |          |           |           |           |           |          |                |           |           |            |

|            |          |           |           |           |           |          |                |           |           |            |

|            |          |           |           |           |           |          |                |           |           |            |

| D Flip Flo | ор       |           |           |           |           |          |                |           |           |            |

| Flip flop  | s are    |           |           | _ sensit  | cive.     |          |                |           |           |            |

|            | sens     | itive: th | ne output | changes   | on the    |          | of             | the enal  | ble signa | al.        |

<sup>©</sup> 2019, Rebecca Rashkin - This document may be copied, redistributed, transformed, or built upon in any format for **educational**, non-commercial purposes. Please give me appropriate credit should you choose to modify this resource. Thank you:)

# Positive Edge-Triggered Flip Flop

| Draw the schematic here: |          |   |    |  |  |  |  |  |

|--------------------------|----------|---|----|--|--|--|--|--|

|                          | WE / CLK | Q | Q' |  |  |  |  |  |

|                          | ↑ 1      |   |    |  |  |  |  |  |

|                          | other    |   |    |  |  |  |  |  |

|                          |          | _ | _  |  |  |  |  |  |

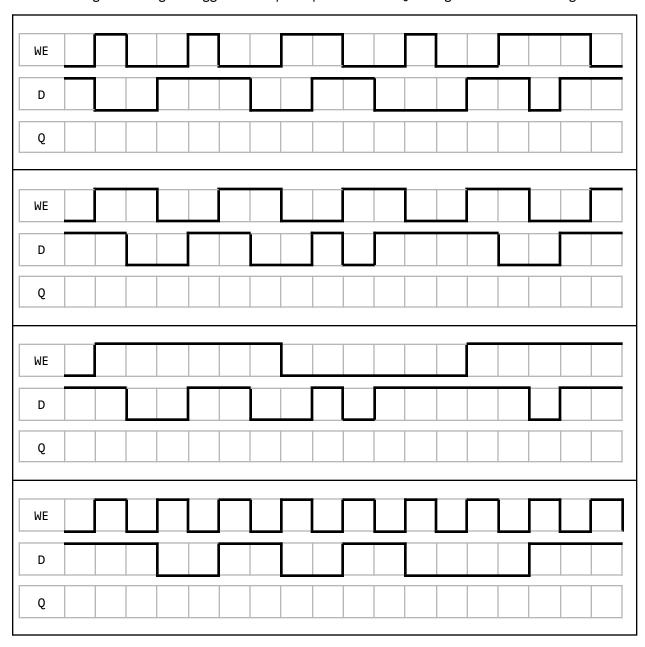

Timing Diagram Examples

Assume a positive edge-triggered flip flop. Fill out Q for given WE and D signals.

|    |  |      |      | _ |  |  |  |  |  |  |

|----|--|------|------|---|--|--|--|--|--|--|

| WE |  |      |      |   |  |  |  |  |  |  |

| D  |  |      |      |   |  |  |  |  |  |  |

| Q  |  |      |      |   |  |  |  |  |  |  |

|    |  | <br> | <br> |   |  |  |  |  |  |  |

| WE |  |      |      |   |  |  |  |  |  |  |

| D  |  |      |      |   |  |  |  |  |  |  |

| Q  |  |      |      |   |  |  |  |  |  |  |

|    |  |      |      |   |  |  |  |  |  |  |

| WE |  |      |      |   |  |  |  |  |  |  |

| D  |  |      |      |   |  |  |  |  |  |  |

| Q  |  |      |      |   |  |  |  |  |  |  |

|    |  |      |      |   |  |  |  |  |  |  |

| WE |  |      |      |   |  |  |  |  |  |  |

| D  |  |      |      |   |  |  |  |  |  |  |

| Q  |  |      |      |   |  |  |  |  |  |  |

<sup>© 2019,</sup> Rebecca Rashkin - This document may be copied, redistributed, transformed, or built upon in any format for **educational**, non-commercial purposes. Please give me appropriate credit should you choose to modify this resource. Thank you:)

# Negative Edge-Triggered Flip Flop

| Draw the schematic here: |          |              |    |

|--------------------------|----------|--------------|----|

|                          | WE / CLK | Q            | Q' |

|                          | ↓ 0      |              |    |

|                          | other    |              |    |

|                          |          | <del>-</del> |    |

Timing Diagram Examples

Assume a negative edge-triggered flip flop. Fill out Q for given WE and D signals.

<sup>© 2019,</sup> Rebecca Rashkin - This document may be copied, redistributed, transformed, or built upon in any format for **educational**, non-commercial purposes. Please give me appropriate credit should you choose to modify this resource. Thank you:)